# Birthing the Computer

# Birthing the Computer:

# From Relays to Vacuum Tubes

Ву

Stephen H. Kaisler, D.Sc.

Cambridge Scholars Publishing

Birthing the Computer: From Relays to Vacuum Tubes Series: Historical Computing Machine Series

By Stephen H. Kaisler, D.Sc.

This book first published 2016

Cambridge Scholars Publishing

Lady Stephenson Library, Newcastle upon Tyne, NE6 2PA, UK

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library

Copyright © 2016 by Stephen H. Kaisler, D.Sc.

All rights for this book reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the copyright owner.

ISBN (10): 1-4438-9778-7 ISBN (13): 978-1-4438-9778-5

# **CONTENTS**

| List of Figures                              | XV  |

|----------------------------------------------|-----|

| List of Tables                               | xix |

| Part I Precursor Machines                    | 1   |

| Chapter One                                  | 3   |

| Konrad Zuse's Computers                      |     |

| 1.1 The Z1                                   | 5   |

| 1.2 The Z2                                   | 6   |

| 1.3 The Z3                                   | 7   |

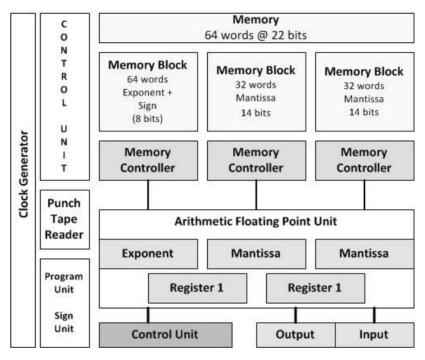

| 1.3.1 Z3 Architecture                        | 9   |

| 1.3.2 Memory                                 | 10  |

| 1.3.3 Floating Point Registers               | 10  |

| 1.3.4 Input and Output                       |     |

| 1.3.5 Instruction Execution                  | 11  |

| 1.3.6 Instruction Set                        | 11  |

| 1.3.7 Programming the Z3                     | 12  |

| 1.3.8 Z3 Assessment                          | 12  |

| 1.4 The Z4                                   | 13  |

| 1.4.1 ETH and the Z4                         | 14  |

| 1.4.2 The Z5                                 | 15  |

| 1.5 Plankalkul                               | 16  |

| 1.6 The Z11                                  | 17  |

| 1.7 The Z22                                  | 19  |

| 1.8 The Z23                                  | 20  |

| 1.9 The Z31                                  | 21  |

| 1.10 Assessment of Zuse's Computing Machines | 22  |

| Chapter Two                                  | 24  |

| The Atanasoff-Berry Computer                 |     |

| 2.1 ABC System Architecture                  | 24  |

| 2.2 The Atanasoff-Mauchly Conflict           |     |

vi Contents

| 2.3 The ABC Reconstructed                     | 28 |

|-----------------------------------------------|----|

| 2.4 ABC Assessment                            | 28 |

| Chapter Three                                 | 20 |

| Stibitz's Relay Computers                     |    |

| 3.1 Model I: The Complex Numerical Calculator | 32 |

| 3.2 Model II: The Relay Interpolator          |    |

| 3.3 Model III: The Ballistic Computer         |    |

| 3.4 Model IV: The Error Detector Mark II      |    |

| 3.5 Model V                                   | 35 |

| 3.6 Model VI                                  |    |

| 3.7 Later BTL Machines                        | 37 |

| 3.8 Assessment of Stibitz's Relay Computers   | 37 |

| Chapter Four                                  | 39 |

| Colossus                                      |    |

| 4.1 Rebuilding Colossus                       | 44 |

| 4.2 Colossus Architecture                     |    |

| 4.3 Colossus and Code Breaking                | 47 |

| 4.4 Assessment of Colossus                    | 49 |

| Chapter Five                                  | 51 |

| Aiken's ASCC/Mark I                           |    |

| 5.1 ASCC System Architecture                  | 54 |

| 5.1.1 Automatic Sequence Unit                 | 54 |

| 5.1.2 Arithmetic Calculations                 | 55 |

| 5.1.3 Interpolators                           |    |

| 5.1.4 Special Registers                       | 56 |

| 5.2 I/O System                                |    |

| 5.3 Programming the ASCC                      |    |

| 5.4 ASCC Assessment                           | 57 |

| Chapter Six                                   | 59 |

| Harvard Mark Machines                         |    |

| 6.1 Mark II                                   | 59 |

| 6.2 Mark III                                  | 61 |

| 6.3 Mark IV                                   |    |

| 6.4 Mark Machines Assessment                  | 63 |

| Birthing the Computer: From Relays to Vacuum Tubes | vii |

|----------------------------------------------------|-----|

|                                                    |     |

|   | ٠ | ٠ |

|---|---|---|

| V | 1 | 1 |

| Chapter Seven                                  | 64 |

|------------------------------------------------|----|

| IBM's Selective Sequence Electronic Calculator |    |

| 7.1 SSEC System Architecture                   | 66 |

| 7.1.1 Electronic Storage Units                 | 67 |

| 7.1.2 Relay Storage                            |    |

| 7.1.3 Tape Storage                             |    |

| 7.1.4 Dial Storage                             |    |

| 7.1.5 Pluggable Storage                        |    |

| 7.1.6 Program Tapes                            | 68 |

| 7.2 SSEC Reliability                           |    |

| 7.3 SSEC Assessment                            |    |

| Chapter Eight                                  | 72 |

| Further Reading                                | 73 |

| Exercises for the Reader                       | 76 |

| Part II                                        | 79 |

| Chapter Nine                                   | 80 |

| ENIAC                                          |    |

| 9.1 ENIAC System Architecture                  | 84 |

| 9.1.1 Accumulators                             | 85 |

| 9.1.2 Control Units                            | 86 |

| 9.1.3 Master Programmer                        |    |

| 9.1.4 Arithmetic Units                         |    |

| 9.1.5 Constant Transmitter                     |    |

| 9.1.6 Function Table                           |    |

| 9.1.7 Input/Output Units                       |    |

| 9.2 Later Modifications                        |    |

| 9.3 Applying ENIAC                             |    |

| 9.4 The ENIAC Women                            |    |

| 9.5 Myths and Stories About ENIAC              |    |

| 9.6 Assessment of ENIAC                        | 91 |

viii Contents

| Chapter Ten                       | 94  |

|-----------------------------------|-----|

| EDVAC                             |     |

| 10.1 The Von Neumann Report       | 95  |

| 10.2 The Patent Dispute           | 97  |

| 10.3 The "Real" EDVAC             | 97  |

| 10.4 EDVAC Architecture           | 99  |

| 10.4.1 System Architecture        | 99  |

| 10.4.2 Memory System              |     |

| 10.4.3 I/O System                 |     |

| 10.4.4 The EDVAC Console          |     |

| 10.4.5 Debugging Support          | 103 |

| 10.5 EDVAC Instruction Set        |     |

| 10.6 Physical Challenges          | 105 |

| 10.7 EDVAC Implementation         |     |

| 10.8 EDVAC Software               | 108 |

| 10.9 EDVAC Applications           |     |

| 10.9.1 EDVAC Operation            |     |

| 10.10 EDVAC Assessment            | 110 |

| Chapter Eleven                    | 111 |

| 11.1 EDSAC System Architecture    | 112 |

| 11.2 The EDSAC Order Code         |     |

| 11.3 Programming the EDSAC        | 116 |

| 11.3.1 Subroutine Libraries       | 117 |

| 11.3.2 The Travails of Paper Tape |     |

| 11.3.3 An EDSAC Simulator         |     |

| 11.4 EDSAC Firsts                 |     |

| 11.5 EDSAC 2                      |     |

| 11.6 EDSAC Assessment             | 122 |

| Chapter Twelve                    | 123 |

| Manchester SSEM                   |     |

| 12.1 The SSEM Architecture        | 127 |

| 12.2 Assessment of the SSEM       |     |

| Chapter Thirteen                  | 130 |

| BINAC                             |     |

| 13.1 System Architecture          |     |

| 13.2 Instruction Set              |     |

| 13.3 BINAC Assessment             |     |

| Chapter Fourteen                     | 134 |

|--------------------------------------|-----|

| Pilot ACE                            |     |

| 14.1 Pilot ACE System Architecture   | 136 |

| 14.2 Programming the Pilot ACE       | 137 |

| 14.3 Pilot ACE Assessment            | 138 |

| 14.4 The ACE                         |     |

| Chapter Fifteen                      | 140 |

| BRLESC                               |     |

| 15.1 BRLESC I                        | 140 |

| 15.2 BRLESC II                       | 143 |

| 15.3 BRLESC Assessment               | 144 |

| Further Reading                      | 146 |

| Exercises for the Reader             | 149 |

| Part III                             | 151 |

| Vacuum Tube Machines                 |     |

| Chapter Sixteen                      | 154 |

| Engineering Research Associates      |     |

| 16.1 ERA 1101 Architecture           | 158 |

| 16.1.1 System Architecture           | 160 |

| 16.1.2 I/O Systems                   | 162 |

| 16.1.3 UNIVAC 1101 Instruction Set   | 162 |

| 16.1.4 The Atlas II                  | 164 |

| 16.2 UNIVAC 1102                     | 164 |

| 16.3 Dissonance at Remington Rand    | 166 |

| 16.4 Assessment of the UNIVAC 1101   | 166 |

| Chapter Seventeen                    | 168 |

| UNIVAC 1103                          |     |

| 17.1 UNIVAC 1103 System Architecture | 168 |

| 17.1.1 Control Components            |     |

| 17.1.2 Arithmetic Registers          | 171 |

| 17.1.3 Master Clock                  |     |

| 17.2 Storage                         |     |

| 17.3 Arithmetic                      |     |

| 17.4 Instruction Format              |     |

| 17.4.1 Transmissive Instructions     |     |

x Contents

| 17.4.2 Replace Instructions                       | 175 |

|---------------------------------------------------|-----|

| 17.4.3 Split Instructions                         | 175 |

| 17.4.4 Q-Controlled Instructions                  | 176 |

| 17.4.5 Sequenced Instructions                     | 176 |

| 17.4.6 One-Way Conditional Jump Instructions      | 178 |

| 17.4.7 Two-Way Conditional Jump Instructions      | 178 |

| 17.4.8 One-Way Unconditional Jump Instructions    |     |

| 17.4.9 External Equipment Instructions            |     |

| 17.4.10 Stop Instructions                         | 180 |

| 17.5 I/O Systems                                  | 180 |

| 17.5.1 I/O Registers                              | 181 |

| 17.5.2 Program Interrupts                         |     |

| 17.6 UNIVAC 1103A                                 |     |

| 17.7 UNIVAC 1104                                  |     |

| 17.8 Assessment of the Early UNIVAC 11xx Machines | 184 |

|                                                   |     |

| Chapter Eighteen                                  | 185 |

| NBS Computing Machines                            |     |

| 18.1 SEAC                                         |     |

| 18.1.1 SEAC System Architecture                   |     |

| 18.1.2 Applications                               |     |

| 18.2 SWAC                                         |     |

| 18.2.1 System Architecture                        |     |

| 18.2.2 Instruction Set                            | 192 |

| 18.2.3 Software                                   |     |

| 18.3 DYSEAC                                       |     |

| 18.4 NBS Computer Assessment                      | 195 |

| Chapter Nineteen                                  | 100 |

| •                                                 | 196 |

| MIT Whirlwind                                     | 100 |

| 19.1 Whirlwind System Architecture                |     |

| 19.1.1 Arithmetic Unit                            |     |

| 19.1.2 Registers                                  |     |

| 19.1.3 Magnetic Core Memory                       |     |

| 19.1.4 Auxiliary Storage                          |     |

| 19.1.5 I/O System                                 |     |

| 19.2 Whirlwind Instruction Set                    |     |

| 19.3 Sample Whirlwind Program                     |     |

| 19.4 Whirlwind Assessment                         | 205 |

| Chapter Twenty                        | 206   |

|---------------------------------------|-------|

| The IAS Machine                       |       |

| 20.1 IAS System Architecture          |       |

| 20.2 IAS Orders                       |       |

| 20.3 Assessment of the IAS            | 211   |

| Chapter Twenty-One                    | 213   |

| MANIAC I                              |       |

| 21.1 MANIAC System Architecture       | 213   |

| 21.2 MANIAC Instruction Set           |       |

| 21.3 Programming the MANIAC           |       |

| 21.4 MANIAC II                        |       |

| 21.4.1 MANIAC II System Architecture  |       |

| 21.4.2 Demand Paging                  |       |

| 21.4.3 Peripherals                    |       |

| 21.5 Chess Playing                    |       |

| 21.6 MANIAC III                       |       |

| 21.6.1 MANIAC III System Architecture |       |

| 21.6.2 MANIAC III Instruction Set     |       |

| 21.7 MANIAC Assessment                |       |

| Chapter Twenty-Two                    | 229   |

| The ORDVAC Computer                   |       |

| 22.1 ORDVAC System Architecture       | 231   |

| 22.1.1 Arithmetic and Control Units   |       |

| 22.1.2 Memory                         |       |

| 22.1.3 I/O Devices                    |       |

| 22.2 Error Checking the ORDVAC        |       |

| 22.3 ORDVAC Instruction Set           |       |

| 22.4 Assessment of ORDVAC             |       |

| Chapter Twenty-Three                  | 241   |

| UNIVAC I                              | 2 . 1 |

| 23.1 UNIVAC I at Lawrence Livermore   | 242   |

| 23.2 Early UNIVAC Orders              |       |

| 23.3 UNIVAC I at the Census Bureau    |       |

| 23.4 UNIVAC I Architecture            |       |

| 23.4.1 UNIVAC I Memory                |       |

| 23.4.2 UNIVAC I I/O                   |       |

| 23.5 UNIVAC I Instruction Set         |       |

| 23.6 UNIVAC I and Programming         |       |

xii Contents

| 23.7 Remington Rand's Problems               | 255 |

|----------------------------------------------|-----|

| 23.8 UNIVAC II                               | 256 |

| 23.9 UNIVAC III                              | 257 |

| 23.10 UNIVAC I-III Assessment                | 260 |

| Chapter Twenty-Four                          | 261 |

| English Electric DEUCE                       |     |

| 24.1 Basic Architecture                      | 263 |

| 24.2 Hardware Configuration                  | 264 |

| 24.3 The Control                             | 265 |

| 24.4 Instruction Highway                     |     |

| 24.5 Main Memory                             | 267 |

| 24.6 The Magnetic Store                      |     |

| 24.7 I/O Devices                             |     |

| 24.8 Instruction Set                         | 269 |

| 24.9 UTECOM                                  |     |

| 24.10 EASICODE                               |     |

| 24.11 Assessment of the DEUCE                | 274 |

| Chapter Twenty-Five                          | 276 |

| Ferranti Pegasus                             |     |

| 25.1 Pegasus Configuration                   | 278 |

| 25.1.1 Control Unit                          |     |

| 25.1.2 The Main Store                        |     |

| 25.1.3 The Computing Store                   |     |

| 25.1.4 Control Panel                         |     |

| 25.1.5 I/O System                            | 281 |

| 25.2 Pegasus Instruction Set                 |     |

| 25.3 Pegasus I at the British Science Museum |     |

| 25.4 Pegasus Assessment                      | 284 |

| Chapter Twenty-Six                           | 285 |

| Ferranti Mark I/II                           |     |

| 26.1 Ferranti Mark I                         |     |

| 26.2 Mark I Architecture                     |     |

| 26.3 Mark I Instruction Set                  |     |

| 26.3.1 Arithmetic and Logical Orders         |     |

| 26.3.2 B-Line Manipulation Orders            |     |

| 26.3.3 Control Transfer Orders               |     |

| 26.3.4 Peripheral and Miscellaneous Orders   | 290 |

| Birthing the Computer: From Relays to Vacuum Tubes | xiii  |

|----------------------------------------------------|-------|

| 26.4 Programming the Ferranti Mark I               | 291   |

| 26.5 Assessment of the Mark I                      |       |

| Chapter Twenty-Seven                               | . 294 |

| Ferranti Mercury                                   |       |

| 27.1 System Architecture                           | 296   |

| 27.2 Instruction Set                               | 296   |

| 27.3 Mercury Autocode                              | 296   |

| 27.4 Mercury Installations                         | 298   |

| 27.5 Assessment of the Ferranti Machines           | 299   |

| Chapter Twenty-Eight                               | 300   |

| Univac File Computers                              |       |

| 28.1 The File 0 Machine                            |       |

| 28.2 The File 1/ File 2 Machines                   | 304   |

| 28.3 Arithmetic and Control Unit                   | 310   |

| 28.4 I/O Systems                                   | 310   |

| 28.4.1 I/O Storage                                 | . 311 |

| 28.4.2 Buffer Storage                              |       |

| 28.4.3 High-Speed Storage                          | 312   |

| 28.4.4 Large Capacity Drum                         | 312   |

| 28.5 File Computer Operations                      | 314   |

| 28.6 File Computer Assessment                      | 316   |

| Chapter Twenty-Nine                                | . 317 |

| IBM 305 RAMAC                                      |       |

| 29.1 RAMAC Origins                                 | 318   |

| 29.2 IBM 305 System Architecture                   | 319   |

| 29.2.1 Processing Unit and Main Memory             | 320   |

| 29.2.2 Input Card Reader                           |       |

| 29.2.3 Output Printer and Punch                    |       |

| 29.2.4 System Console                              |       |

| 29.3 Instruction Format                            | 323   |

| 29.3.1 Accumulators                                |       |

| 29.4 Controlling the IBM 305                       | 325   |

| 29.5 IBM 350 Disk File                             | 328   |

| 29.6 IBM 305 Assessment                            | 328   |

| Further Reading                                    | 330   |

| Exercises for the Reader                           | . 333 |

| xiv | Contents |

|-----|----------|

|     |          |

| Glossary   | 335 |

|------------|-----|

| References | 337 |

| Index      | 349 |

# LIST OF FIGURES

Note: U. S. Government photographs are public domain information.

| 1-1        | Z1 Architecture                                                                  |  |

|------------|----------------------------------------------------------------------------------|--|

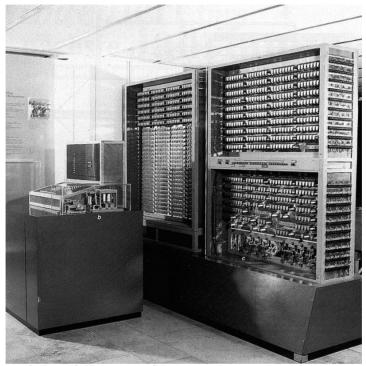

| 1-2        | Zuse Z3 (Reconstructed)                                                          |  |

| 1-3        | Architecture of the Zuse Z3                                                      |  |

| 1-4        | Z11 Console                                                                      |  |

| 1-5        | Z22 at the University of Applied Sciences, Karlsruhe,                            |  |

| 1-6        | Z23                                                                              |  |

| 1-7        | Z31 Computer                                                                     |  |

| 2-1        | The Atanasoff-Berry Computing Machine                                            |  |

| 4-1        | Lorenz Machine,                                                                  |  |

| 4-2        | Main House at Bletchley Park                                                     |  |

| 4-3        | A Colossus Mark 2,                                                               |  |

| 4-4        | Colossus MkII Paper Tape Reader                                                  |  |

| 5-1        | The Automatic Sequence Controlled Calculator                                     |  |

| 6-1<br>6-2 | Harvard Mark III at U.S. Navy Installation<br>Harvard Mark III Operators Console |  |

| 7-1<br>7-2 | IBM SSEC System Architecture IBM SSEC Sequence Formats                           |  |

| 9-1        | The ENIAC                                                                        |  |

| 9-2        | ENIAC System Architecture                                                        |  |

| 9-3        | The ENIAC Women                                                                  |  |

| 9-4        | Programming the ENIAC                                                            |  |

| 9-5        | 50 Years of Computer Technology Commemoration Stamp                              |  |

| 10-1       | The EDVAC                                                                        |  |

| 10-2       | Mercury Delay Line Structure                                                     |  |

| 11-1       | EDSAC 1 <sup>st</sup> Operation Entry                                            |  |

| 11-2       | EDSAC Early Configuration                                                        |  |

- 11-3 EDSAC System Architecture

- 11-4 EDSAC Simulator Interface

- 12-1 Small Scale Experimental Machine

- 12-2 SSEM Replica

- 12-3 SSEM System Architecture

- 14-1 Pilot ACE Computer at the National Physical Laboratory

- 14-2 Pilot Ace Instruction Format

- 15-1 BRLESC Console

- 15-2 BRLESC I Figure

- 15-3 BRLESC I Cabinets

- 15-4 BRLESC Instruction Format

- 16-1 An Early View of ERA 1101 Console

- 16-2 ERA 1101 Console

- 16-3 ERA 1101 Computer (aka Atlas)

- 16-4 ERA 1101 System Architecture

- 16-5 UNIVAC 1102 at Arnold Engineering Center

- 16-6 UNIVAC 1102 Computer System

- 17-1 UNIVAC 1103 System Architecture

- 17-2 UNIVAC 1103 Accumulator Register

- 17-3 UNIVAC 1103 Instruction Format

- 18-1 NBS SEAC Computer System

- 18-2 SEAC Instruction Format

- 18-3 The Standards Eastern Automatic Computer

- 18-4 SWAC Dedication Pamphlet (Front Page)

- 18-5 Harry Huskey at the SWAC Console

- 19-1 Example Use of Oscilloscope

- 19-2 Whirlwind Instruction Format

- 20-1 IAS System Architecture

- 20-2 IAS CPU Architecture

- 20-3 IAS Instruction Format

- 21-1 MANIAC I Computer System

- 21-2 MANIAC Racks

- 21-3 MANIAC Programming Integration via Simpson's Rule

- 21-4 MANIAC Example Box 1

- 21-5 MANIAC Example Box 9

- 21-6 MANIAC II

- 21-7 MANIAC III Instruction Format

- 21-8 MANIAC III System Architecture

- 21-9 MANIAC III Instruction Format

- 22-1 The ORDVAC Computer

- 22-2 ORDVAC System Architecture

- 22-3 ORDVAC Registers

- 22-4 ORDVAC Instruction Format

- 23-1 UNIVAC I on Election Night 1952

- 23-2 UNIVAC I Computer System

- 23-3 UNIVAC I Operator Console

- 23-4 MATH-MATIC Brochure

- 23-5 FLOW-MATIC Brochure

- 23-6 Sample Program in FLOW-MATIC

- 23-7 UNIVAC II Computer System

- 23-8 UNIVAC III Instruction Format,

- 24-1 English Electric DEUCE Brochure Cover

- 24-2 EASICODE Programming Example

- 25-1 Pegasus Main Cabinet

- 25-2 Pegasus Instruction Format

- 25-3 Pegasus Operating

- 25-4 Pegasus Simulator

- 26-1 Mark I Instruction Format

- 26-2 Mark I Drum Transfer Instruction

- 27-1 Ferranti Mercury Core Board

- 27-2 Ferranti Mercury

- 28-1a UNIVAC File Computer Ad, 1956

- 28-1b UNIVAC File Computer Ad, circa 1956

- 28-2 UNIVAC File Computer Advertisement, circa 1960

- 28-3 Remington Rand File Computer System Architecture

| 28-4 | UNIVAC File Computer – High-Speed Drum Layout     |

|------|---------------------------------------------------|

| 28-5 | UNIVAC File Computer – Large Capacity Drum Access |

|      |                                                   |

| 29-1 | IBM 305 RAMAC                                     |

| 29-2 | IBM 305 RAMAC at U.S. Army Red River Arsenal      |

| 29-3 | IBM 305 – Sample Data Transfer Instruction        |

| 29-4 | IBM 380 System Console                            |

| 29-5 | IBM 380 Front Panel                               |

| 29-6 | IBM 305 Instruction Format                        |

| 29-7 | IBM 305 Process Control Panel                     |

|      |                                                   |

List of Figures

xviii

# LIST OF TABLES

| 1-2  | Z3 Instruction Set                        |

|------|-------------------------------------------|

| 1-3  | Z4 – Basic Characteristics                |

| 1-4  | Z5 – Basic Characteristics                |

| 1-5  | Zuse Z11 – Basic Characteristics          |

| 1-6  | Z22 – Basic Characteristics               |

| 1-7  | Z23 – Basic Characteristics               |

| 3-1  | Model V – Basic Characteristics           |

| 6-1  | Mark II – Basic Characteristics           |

| 6-2  | Mark III – Basic Characteristics          |

| 7-1  | SSEC Characteristics                      |

| 7-2  | S1 Sequence Fields                        |

| 7-3  | S2 Sequence Fields                        |

| 9-1  | ENIAC – Basic characteristics             |

| 10-1 | EDVAC – Basic Characteristics             |

| 10-2 | EDVAC Instruction Set                     |

| 11-1 | EDSAC – Basic Instructions                |

| 11-2 | EDSAC Order Code                          |

| 11-3 | EDSAC 2 – Basic Characteristics           |

| 12-1 | Manchester Mark I – Basic Characteristics |

| 12-2 |                                           |

| 13-1 | BINAC Characteristics                     |

| 13-1 |                                           |

| 13-2 | DINAC HISHUCHOH SEL                       |

| 14-1 | Pilot ACE – Basic Characteristics         |

| 15-1 | BRLESC I – Basic Characteristics          |

| 15.2 | DDI ECC II Desig Characteristics          |

1-1 Zuse Z3 – Basic Characteristics

xx List of Tables

- 16-1 ERA 1101/UNIVAC I Basic Characteristics

- 16-2 UNIVAC 1101 Instruction Set

- 16-3 UNIVAC 1102 Basic Characteristics

- 17-1 UNIVAC 1103 Basic Characteristics

- 17-2 UNIVAC 1103 Registers

- 17-3 UNIVAC 1103 Transmissive Instructions

- 17-4 UNIVAC 1103 Replace Instructions

- 17-5 UNIVAC 1103 Shift Instructions

- 17-6 UNIVAC 1103 O-Controlled Instructions

- 17-7 UNIVAC 1103 Sequenced Instructions

- 17-8 UNIVAC 1103 One-Way Conditional Jump Instructions

- 17-9 UNIVAC 1103 Two-Way Conditional Jump Instructions

- 17-10 UNIVAC 1103 One-Way Unconditional Jump Instructions

- 17-11 UNIVAC 1103 External Equipment Instructions

- 17-12 UNIVAC 1103 Stop Instructions

- 18-1 SEAC Basic Characteristics

- 18-2 DYSEAC Basic Characteristics

- 19-1 Whirlwind Basic Characteristics

- 19-2 Whirlwind I/O Instructions

- 19-3 Other Whirlwind Instructions

- 20-1 IAS Characteristics

- 20-2 IAS Registers

- 20-3 IAS Instruction Set

- 21-1 MANIAC Basic Characteristics

- 21-2 MANIAC Instruction Set

- 21-3 MANIAC II Basic Characteristics

- 21-4 MANIAC III Basic Characteristics

- 21-5 MANIAC III Inflectors

- 22-1 ORDVAC Characteristics

- 22-2 ORDVAC Orders

- 23-1 UNIVAC I Basic Characteristics

- 23-2 UNIVAC I Deliveries

- 23-3 UNIVAC I Instruction Set

- 23-4 UNIVAC III Basic Characteristics

- 24-1 DEUCE Basic Characteristics

- 24-2 Delay Line Layout

- 24-3 EASICODE Orders

- 25-1 Pegasus Basic Characteristics

- 25-2 Pegasus Special Registers

- 26-1 Ferranti Mark I Characteristics

- 26-2 Mark I Arithmetic and Logical Orders

- 26-3 Mark I B-Line Orders

- 26-4. Mark I Control Transfer Orders

- 26-5 Mark I Peripheral and Miscellaneous Instructions

- 26-6 The Base-32 Table

- 27-1 Mercury Basic Characteristics

- 28-1 UNIVAC File 0 Computer Basic Characteristics

- 28-2 UNIVAC File 1 Computer Basic Characteristics

- 28-3 File 1 Computer Program Steps

- 28-1 File 1 Computer Instruction Words

- 29-1. Magnetic Drum Track Assignments

- 29-2 IBM 305 Instruction Format Description

### PART I

### PRECURSOR MACHINES

#### Chapters 1 to 8

The idea of automated computation has been a concept in the human mind for several thousand years. Discoveries of ancient machines, such as the Antikythera mechanism, reveal that our ancestors had some understanding of the basic concepts of computation, although contemporary technology was not up to the task of performing such computations.

The true history of computing begins in the early 1900s. These early days were largely characterized by electromechanical computing engines rather than true computing systems. However, these systems were replaced in the late 40s and early 50s by vacuum tube machines. The machines discussed here are considered by some not to be true computers because they did not have a provision for storing programs internally. Others, however, do not make such a distinction as they consider such machines to have their primary storage only in external media, e.g., paper tape and magnetic tape. There is no benefit in continuing that debate here and we will not do so.

By the 1930s, after Hollerith's success with tabulating machines, several companies, such as Burroughs (manufacturing calculators) and National Cash Register (manufacturing cash registers), understood the elements of computing. The time seemed ripe for someone to put the pieces together and realize that the process could be automated. Konrad Zuse, John Atanasoff, and George Stibitz were among those people. In England, Alan Turing, aided by Max Newman, Tommy Flowers, and a host of other dedicated civil servants, developed and implemented the Colossus. In the United States, Howard Aiken also realized the utility of automating computation and developed several machines that contributed to a better understanding of how to build computing systems. Finally, IBM was transforming lessons learned from the ASCC into one of its first true computing systems, IBM 650.

2 Part I

The film, Computer Pioneers and Pioneer Computers: Dawn of Electronic Computing: 1935-1945, narrated by Gordon Bell and produced by the Computer History Museum, provides some photos and videos of the machines described in this section.

#### Chapters:

- 1. Konrad Zuse's Computers

- 2. The Atanasoff-Berry Computer

- 3. Stibitz's Relay Computers

- 4. Colossus

- 5. Aiken's ASCC/Mark I

- 6. Harvard Mark Machines

- 7. IBM's Selective Sequence Electronic Calculator

- 8. Who invented the Computer?

### CHAPTER ONE

### KONRAD ZUSE'S COMPUTERS

Konrad Zuse was one of the "fathers of computing" (Rojas, Speiser, and Zuse 2001). Zuse built several different computing machines – each of increasing complexity and capability. He also created one of the first companies whose sole purpose was to build computing machines.

Zuse started his career working for the German aviation industry. As an engineer, he was familiar with the large number of calculations required to analyze and design the static structures of an aircraft. This led him to think about how he could mechanize some of these monotonous and repetitive calculations. He reasoned that a machine should be able to follow a set of carefully laid out steps in a repetitive fashion. He envisioned that numbers would be entered from an input unit and that results would be placed in an output unit to be read.

The computing machine would be comprised of a memory (*Speicherwerk*), an arithmetic unit (*Rechenwerk*), and a control unit (*Programwerk*). Arithmetic would be performed using a floating point representation, with separate units for handling the exponent and fraction. Numbers and instructions would be represented in the binary number system. The control unit would move the numbers into and out of the memory and specified what arithmetic operations were to be performed. The instructions and numbers would be stored on a strip of punched tape (*Lochstreifen*).

The machine's components would be synchronized by a central clock. Zuse recognized that all operations could be performed logically from combinations of the Boolean operators AND, OR, and NOT. To follow his dream, Zuse quit his job in 1936 in order to develop his ideas further.

#### Konrad Zuse (1910-1996)

Konrad Zuse was born in Berlin in 1910. He earned his technical education at the Technische Hochschule in Berlin-Charlottenburg, where he majored in architecture and civil engineering. By 1933, he had begun to think about how to build a universal computing machine. As noted below, he developed several models of computing machines through the war

years. At the end of World War II, he founded Zuse Ingenieurboro, Hopferau bei Fussen. Throughout the 1950s, he developed new computers under a contract with Remington Rand. In 1967, he sold Zuse KG to Siemens Corporation and became a professor at the University of Gottingen. He designed one of the first programming languages, Plankalkul. Zuse received many accolades and awards, including the AFIPS Harry Goode Memorial Award in 1965 and the IEEE Computer Pioneer Medal in 1982. The picture below depicts Konrad Zuse circa 1992.

Source: Courtesy of Dr.- Dr.-Ing. Habil. Horst Zuse

In 1949, Zuse formed Zuse KG to design and manufacture digital computers. Over the next 18 years, Zuse KG delivered over 250 computers. However, it had neither the size nor resources to compete with several English and US companies, which had begun to sell to European universities and companies. In 1967, Zuse sold his company to Siemens after it encountered financial problems.

#### 1.1 The Z1

After graduation in 1931, Zuse became a structural engineer with Henschel Flugzeugwerke, but left soon after to pursue his ideas regarding the development of an electromechanical computer. He had not been trained in mechanical calculator construction. This allowed him to pursue his own ideas which represented an original approach unhindered by what the experts said could and could not be done. He designed and assembled this machine, the Z1 in his parent's apartment in Berlin with financing from his parents and various school friends (Weiss 1996).

Zuse's first computing machine was the electromechanical Z1, which demonstrated the limits of mechanical computing systems. It was about the size of a large dining room table. The Z1 used mechanical bistable switching elements for memory and arithmetic/logical circuits. The elements were represented by pins arranged in matrices to signify bit positions. A stack of metal sheets with slots moved over the pins to read data from the memory. The movement of a sheet depended on the positions of the pins in the slots. Zuse enlisted several friends to hand-cut the holes in the metal plates with an electric saw. By 1938, Zuse had a working model of the Z1 that represented sixteen 24-bit numbers and performed floating point binary arithmetic.

However, this machine did not work very well because of the difficulty of precisely hand-machining the parts and having them work together reliably. The memory worked well, but the arithmetic unit was unreliable. The Z1 architecture is depicted in Figure 1-1.

Figure 1-1. Z1 Architecture Source: Adapted from

http://user.cs.tu-berlin.de/~zuse/Konrad Zuse/en/rechner z1.html

#### 1.2 The **Z**2

Source: http://user.cs.tu-berlin.de/~zuse/Konrad Zuse/en/rechner z2.html

The Z2, an enhanced version of the Z1, was designed by Konrad Zuse and Helmut Schreyer and completed in 1939 (Deutsche Teknik Museum 2005a). It was an experimental electromechanical machine that used electronic relays, which were more reliable. However, Zuse retained the mechanical memory of the Z1 in the Z2 implementation. The Z2 used 16-bit words and had a cycle time of about 3 seconds. It required about 8 seconds for an addition.

At the beginning of World War II, Zuse was called up for military duty as an infantryman just as he was completing the Z2. He tried to gain official support for his ideas, but these were often dismissed by the German government. After a year's service, he was discharged from the

German Army and he returned to Henschel Flugzeugwerke as a structural engineer. While continuing development of the Z2, he convinced the German Aeronautical Research Institute (Deutsche Versuchsanstalt für Luftfahrt) in 1940 to fund the development of another machine, the Z3.

#### 1.3 The **Z**3

Source: http://www.horst-zuse.homepage.t-online.de/Konrad\_Zuse\_index\_english\_html/rechner z3.html

The Zuse Z3 was completed in 1941. It was based on electromagnetic relays, making it the first functional programmable computer. The Z3 performed about 4 additions per second and required about 5 seconds to perform a multiplication. A program was entered using movie film with eight-hole channels being punched in the reel to represent instructions. The Z3 was one of the first machines to have registers – two floating point registers R1 and R2 – for holding operands for arithmetic operations.

The German Aircraft Research Institute used it to perform statistical analyses of wing flutter. On 12 May 1941, the Z3 was presented to an audience of scientists, including professors Alfred Teichmann and Curt Schmieden of the Deutsche Versuchsanstalt für Luftfahrt in Berlin (KZIA 2015).

In 1960, Zuse KG recreated the Z3 for the Deutsche Museum. Figure 1-2 shows the reconstructed Z3 on display at the Deutsche Museum in Munich (Deutsche Teknik Museum 2005c). The left frame contained the relays for the memory – 64 words of 22 bits each. At the bottom of the right frame one can see the micro-sequencers for instruction execution. They are the core of the Z3's control unit. The frame above them contained the relays for the arithmetic units.

The Z3 was built as a floating point machine. Burks, Goldstine, and von Neumann (1946) questioned whether floating point provided any advantage in performing arithmetic computations given the loss of memory capacity due to the increased number of bits required to represent floating point numbers and the complexity of the electronic circuits required to perform the arithmetic. The types of computations that Zuse was interested in performing with his machines necessitated floating point number representation. Software routines were exceedingly slow to execute and, perhaps, too large to fit in the available memory. What many do not realize is that Zuse had described the concepts of floating point arithmetic in 1934, more than a decade before Burks et al., and, in the Z3,

Zuse implemented his concept and demonstrated its feasibility. Table 1-1 describes the characteristics of the Z3.

Figure 1-2. Zuse Z3 (Reconstructed) Source: Courtesy of Dr.- Dr.-Ing. Habil. Horst Zuse

Table 1-1. Zuse Z3 – Basic Characteristics

| Characteristic      | Value/Explanation                            |

|---------------------|----------------------------------------------|

| Internal            | Floating Point Binary                        |

| Representation      |                                              |

| # Bits/Word         | 22                                           |

| # Instructions/Word | 1                                            |

| # Instructions      | 9                                            |

| # Bits/Instruction  | 22                                           |

| Instruction Type    | One Address (?)                              |

| CPU Technology      | Electromagnetic Relays: Clock Rate = 5.33 Hz |

| CPU Registers       | Two Floating Point Registers: R1 and R2      |

| Main Memory         | Electromagnetic Relays: 64 words             |