# Simulation and Modeling of Emerging Devices

# Simulation and Modeling of Emerging Devices:

Tunnel Field-Effect and Fin Field Effect Transistors

By

Brinda Bhowmick, Rupam Goswami and Rajesh Saha

Cambridge Scholars Publishing

Simulation and Modeling of Emerging Devices: Tunnel Field-Effect and Fin Field Effect Transistors

By Brinda Bhowmick, Rupam Goswami and Rajesh Saha

This book first published 2023

Cambridge Scholars Publishing

Lady Stephenson Library, Newcastle upon Tyne, NE6 2PA, UK

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library

Copyright © 2023 by Brinda Bhowmick, Rupam Goswami and Rajesh Saha

All rights for this book reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the copyright owner.

ISBN (10): 1-5275-0702-5 ISBN (13): 978-1-5275-0702-9

# **TABLE OF CONTENTS**

| List of | Figures                                            | vii |

|---------|----------------------------------------------------|-----|

| List of | Tables                                             | xi  |

| List of | Symbols                                            | xii |

| Chapt   | er 1 Introduction                                  | 1   |

| 1.1     | Introduction                                       |     |

| 1.2     | Short Channel Effects                              |     |

| 1.3     | Scaling Rules in MOSFETs                           |     |

| 1.4     | Control of SCEs in MOSFETs                         |     |

| 1.5     | Tunnel FET                                         |     |

| 1.6     | FinFET                                             |     |

|         | References                                         |     |

| Chapt   | er 2 Device Architectures: TFETs and FINFETs       | 16  |

| 2.1     | Introduction                                       |     |

| 2.2     | TFET Architectures                                 |     |

| 2.3     | FinFET Architectures                               |     |

|         | References                                         |     |

| Chapt   | er 3 Simulation Methodologies for Emerging Devices | 33  |

| 3.1     | Introduction                                       |     |

| 3.2     | Models for TFETs and FinFETs                       |     |

| 3.2.1   | Fowler–Nordheim Tunneling                          |     |

| 3.2.2   | Direct Tunneling                                   |     |

| 3.2.3   | Nonlocal Band-To-Band Tunneling                    |     |

| 3.2.4   | Fermi-Dirac Statistics                             |     |

|         | Bandgap Narrowing                                  |     |

| 3.2.6   | Shockley-Read-Hall Recombination                   |     |

| 3.2.7   | Mobility Models                                    |     |

|         | References                                         |     |

|         |                                                    |     |

| Chapt  | er 4 Impact of Work Function Variability of Metal Gate | 42  |

|--------|--------------------------------------------------------|-----|

| for En | nerging Devices                                        |     |

| 4.1    | Introduction                                           |     |

| 4.2    | Modeling of Metal Gate WFV                             |     |

| 4.3    | Considering Only Two-Grain Orientation                 |     |

| 4.4    | Considering Only Three-Grain Orientation               |     |

| 4.5    | Simulation Set-up used in TCAD                         |     |

| 4.6    | Impact of WFV on Emerging Devices                      |     |

|        | References                                             |     |

| Chapt  | er 5 Analytical Models for TFETs and FINFETs           | 61  |

| 5.1    | Introduction                                           |     |

| 5.2    | Analytical Models for TFETs                            |     |

| 5.3    | Analytical Models for FinFET                           |     |

|        | References                                             |     |

| Chapt  | er 6 Fabrication of Emerging Devices                   | 95  |

| 6.1    | Introduction                                           |     |

| 6.2    | Esaki Tunnel Diode                                     |     |

| 6.3    | Tentative Process Steps for SOI TFETs                  |     |

| 6.4    | Homojunction TFETs                                     |     |

| 6.5    | SOI Hetero-Gate TFETs                                  |     |

| 6.6    | Survey on Fabrication of FinFET                        |     |

| 6.7    | Proposed Fabrication Process of Step-FinFET            |     |

|        | References                                             |     |

| Chapt  | er 7 Applications of TFETs and FinFETs                 | 109 |

| 7.1    | Introduction                                           |     |

| 7.2    | TFET as a Digital Inverter                             |     |

| 7.3    | TFET as Dielectric Modulated Biosensor                 |     |

| 7.4    | FinFET as Digital Inverter                             |     |

|        | References                                             |     |

|        |                                                        |     |

# LIST OF FIGURES

| Figures    | Captions/Descriptions                                | Page No. |

|------------|------------------------------------------------------|----------|

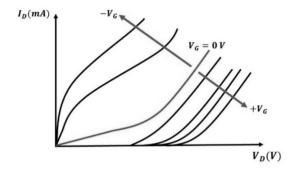

| Figure 1.1 | Current-Voltage characteristics of a MOSFET          | 2        |

|            | with (dotted) and without (solid) channel-           |          |

|            | length modulation for different gate voltages        |          |

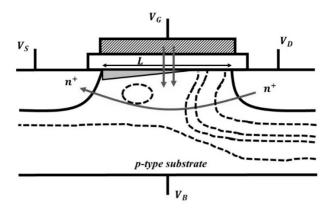

| Figure 1.2 | Two-dimensional schematic of a MOSFET                | 3        |

|            | showing the parameters responsible for               |          |

|            | threshold voltage roll-off                           |          |

| Figure 1.3 | Effect of DIBL on conduction band edge               | 4        |

| Figure 1.4 | The threshold voltage roll-off with gate length      | 4        |

| Figure 1.5 | Effect of punchthrough                               | 5        |

| Figure 1.6 | Tunneling leakage currents                           | 6        |

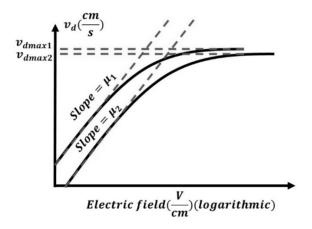

| Figure 1.7 | Velocity saturation effect is shown                  | 7        |

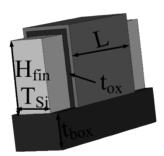

| Figure 1.8 | Three-dimensional view of conventional               | 12       |

|            | FinFET                                               |          |

| Figure 2.1 | Geometry of a conventional TFET                      | 17       |

| Figure 2.2 | Architectures of TFETs: (a) Double-Gate TFET,        | 20-21    |

|            | (b) Dual Dielectric TFET, (c) Gate-Drain             |          |

|            | Underlap-TFET, (d) Stack Gate Dielectric TFET,       |          |

|            | (e) Dual Material Gate TFET, (f) Asymmetric          |          |

|            | Gate Oxide TFET, (g) Wedge-Gate TFET, (h) U-         |          |

|            | shaped Gate TFET, (i) Circular Gate TFET, (j)        |          |

|            | Heterojunction-TFET                                  |          |

| Figure 2.3 | Three-dimensional view of step-FinFET                | 27       |

| Figure 3.1 | Various nonlocal tunneling currents                  | 37       |

| Figure 4.1 | Schematic of a hypothetical metal gate               | 43       |

|            | consisting of grains with three different            |          |

|            | orientations                                         |          |

| Figure 4.2 | WF distribution for hypothetical metal gates         | 45       |

|            | with two-grain orientations composed of (a)          |          |

|            | N = 1, (b) $N = 4$ , (c) $N = 18$ , and (d) $N = 32$ |          |

|            | grains                                               |          |

| Figure 4.3 | WF distribution obtained from model for square shape grain size (a) 30nm*30nm and                                                                                            | 47    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|            | (b) 40nm*40nm                                                                                                                                                                |       |

| Figure 4.4 | Distribution of WF within the top metal gate area                                                                                                                            | 48    |

| Figure 4.5 | Variation in threshold voltage with channel length                                                                                                                           | 53    |

| Figure 4.6 | Comparison of frequency distribution in threshold voltage between Ge and Si FinFETs                                                                                          | 54    |

| Figure 4.7 | (a) Variation in threshold voltage vs. channel length and (b) Variation in threshold voltage vs. channel width                                                               | 55    |

| Figure 5.1 | Geometry of a hetero double-gate dielectric TFET                                                                                                                             | 63    |

| Figure 5.2 | Surface potential for the proposed device at 20 nm gate length                                                                                                               | 67    |

| Figure 5.3 | Variation of horizontal component of electric field (E <sub>x</sub> ) along channel, y=5 nm                                                                                  | 67    |

| Figure 5.4 | Variation of vertical component of electric field $(E_v)$                                                                                                                    | 67    |

| Figure 5.5 | Plot of surface potential versus lateral position at drain voltage 0.5 V for a TFET with channel length 40 nm                                                                | 69    |

| Figure 5.6 | Comparison of threshold voltages from TCAD tool and the algorithm for (a) drain voltage, (b) gate oxide thickness, (c) channel length and (d) different device architectures | 72    |

| Figure 5.7 | (a) three-dimensional view of SOI FinFET, (b) two-dimensional view of SOI FinFET, and (c) SOI FinFET is separated into asymmetric DG and symmetric DG MOSFETs                | 73-74 |

| Figure 5.8 | Variation of surface potential of SOI FinFET for L=30 nm, $T_{si}$ =14 nm, $H_{fin}$ = 20 nm and $t_{ox}$ = 2 nm                                                             | 81    |

| Figure 5.9 | Variation of (a) threshold voltage vs. channel length and (b) threshold voltage vs. fin thickness for L=30 nm, $T_{si}$ =14 nm, $H_{fin}$ = 20 nm and $t_{ox}$ = 2 nm        | 81    |

| Simulation  | and Modeling of Emerging Devices: Tunnel Field-Effect and Fin Field Effect Transistors                                                                               | ix      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 5.10 | Variation of (a) subthreshold swing vs. channel length and (b) SS vs. fin thickness for L=30 nm, $T_{si}$ =14 nm, $H_{fin}$ = 20 nm and $t_{ox}$ = 2 nm              | 81      |

| Figure 5.11 | Variation of probability density function of SOI FinFET for L=10 nm, $T_{si}$ =6 nm, $H_{fin}$ = 10 nm and $t_{ox}$ = 2 nm                                           | 89      |

| Figure 5.12 | Variation of (a) threshold voltage vs. channel length and (b) threshold voltage vs. fin thickness for L=10 nm, $T_{si}$ =6 nm, $H_{fin}$ = 10 nm and $t_{ox}$ = 2 nm | 90      |

| Figure 6.1  | Process flow of homojunction-TFETs                                                                                                                                   | 101     |

| Figure 6.2  | General proposed process flow to fabricate the hetero dielectric stack gate SOI TFET                                                                                 | 103     |

| Figure 6.3  | Process flow to fabricate the step-FinFET                                                                                                                            | 105-106 |

| Figure 7.1  | Transfer characteristics of p-TFET and n-TFET at different temperatures at V <sub>DS</sub> =0.7V                                                                     | 110     |

| Figure 7.2  | $I_{\mbox{\scriptsize d}}\mbox{-}V_{\mbox{\scriptsize g}}$ characteristics at 300K for p-TFET and n-TFET                                                             | 110     |

| Figure 7.3  | Effect of gate oxide charge density for gate on source structures on transfer characteristics of p-TFET and n-TFET at room temperature at V <sub>DS</sub> =0.7V      | 111     |

| Figure 7.4  | Schematic of a C-TFET inverter with a capacitive load at output                                                                                                      | 111     |

| Figure 7.5  | Input output transient characteristics at different high-k gate length                                                                                               | 112     |

| Figure 7.6  | VTC of complementary TFET inverter for different ferroelectric layer thickness, t <sub>FE</sub>                                                                      | 113     |

| Figure 7.7  | Transient characteristics of complementary ferroelectric TFET inverter for different ferroelectric thickness of 12 nm, 9 nm and 6nm                                  | 113     |

| Figure 7.8  | Transient characteristics of complementary ferroelectric TFET inverter for different types of buffer SiO2 and HfO2                                                   | 114     |

| Figure 7.9  | Power-delay product (PDP) at different ferroelectric thickness                                                                                                       | 115     |

| Figure 7.10 | (a) two-dimensional schematic of the circular | 117 |

|-------------|-----------------------------------------------|-----|

|             | gate TFET; (b) transfer characteristics for   |     |

|             | increasing dielectric constant of             |     |

|             | biomolecules; (c) surface potential versus    |     |

|             | lateral position for different dielectric     |     |

|             | constants of biomolecules and (d) sensitivity |     |

|             | versus negative charge of biomolecules        |     |

| Figure 7.11 | Three-dimensional view of the SiGe source     | 118 |

|             | step-FinFET                                   |     |

| Figure 7.12 | Implementation of digital inverter using      | 118 |

|             | FinFET                                        |     |

| Figure 7.13 | Transfer characteristics of conventional,     | 119 |

|             | GaAs, and step-FinFETs                        |     |

| Figure 7.14 | Comparison of transient characteristics       | 120 |

|             | among complementary FinFETs using             |     |

|             | conventional, GaAs, and Step-FinFETs          |     |

| Figure 7.15 | Impact of Ge mole fraction on (a) drain       | 121 |

|             | current, (b) energy bandgap, and (c) gate     |     |

|             | capacitance in SiGe source step-FinFET        |     |

| Figure 7.16 | The impact of Ge mole fraction on voltage     | 122 |

|             | transfer in SiGe source step-FinFET           |     |

# LIST OF TABLES

| Tables    | Captions/Descriptions                                    | Page No |

|-----------|----------------------------------------------------------|---------|

| Table 1.1 | Scaling rules for CMOS technology. Note that             | 9       |

|           | $\alpha$ and $\lambda$ denote the geometry and voltage   |         |

|           | scaling factors                                          |         |

| Table 2.1 | Modes of operation in-TFET, convention of                | 17      |

|           | source and drain regions and biasing                     |         |

|           | conditions                                               |         |

| Table 3.1 | Coefficients for direct tunneling                        | 35      |

| Table 3.2 | Masetti model with default coefficients                  | 41      |

| Table 4.1 | Possible values for probability and WF of a              | 45      |

|           | metal gate consisting of four square size                |         |

|           | grains with two orientation                              |         |

| Table 4.2 | Physical properties of different metal nitrides          | 47      |

|           | used to estimate the effect of grain                     |         |

|           | orientation on the WFV of metal gate.                    |         |

| Table 6.1 | Material and process parameters                          | 97      |

| Table 7.1 | DC analysis of complementary ferroelectric               | 113     |

|           | SBTFET inverter for different ferroelectric              |         |

|           | thickness at fixed C <sub>L</sub> =0.42 fF               |         |

| Table 7.2 | Delay parameters of complementary                        | 114     |

|           | ferroelectric TFET inverter for different buffer         |         |

|           | type                                                     |         |

| Table 7.3 | Delay parameters of complementary                        | 115     |

|           | ferroelectric SBTFET inverter for different              |         |

|           | ferroelectric thickness at fixed C <sub>L</sub> =0.42 fF |         |

| Table 7.4 | Comparison of delay parameters among                     | 120     |

|           | conventional, step, and GaAs FinFETs                     |         |

| Table 7.5 | Effect of mole fraction on noise margin in               | 122     |

|           | SiGe source step-FinFET                                  |         |

# LIST OF SYMBOLS

| Symbol                        | Description               | Symbol                           | Description                    |

|-------------------------------|---------------------------|----------------------------------|--------------------------------|

| $V_{DS}$                      | Drain to source           | k                                | Boltzmann                      |

|                               | voltage                   | _                                | constant                       |

| $V_{GS}$                      | Gate to source voltage    | $I_{on}$                         | On current                     |

| $V_G$                         | Gate voltage              | $I_{o\!f\!f}$                    | Off current                    |

| $V_{FB}$                      | Flat band voltage         | x                                | Mole fraction, Position        |

| $E_g$                         | Band gap energy           | $E_c$                            | Conduction<br>Energy           |

| $I_D$                         | Drain current             | $C_L$                            | Load Capacitance               |

| $V_T, V_{th}$                 | Threshold voltage         | SS                               | Subthreshold swing             |

| $L, L_g$                      | Channel length            | $\sigma V_T, \sigma V_{th}$      | Variation in threshold voltage |

| E                             | Electron wave             | $\sigma SS$                      | Variation in                   |

|                               | energy                    |                                  | subthreshold<br>swing          |

| $\psi_{S, \min}$              | Minimum surface potential | $\sigma I_{on}$                  | Variation in on<br>current     |

| $\psi_{\scriptscriptstyle S}$ | Surface Potential         | $\sigma I_{o\!f\!f}$             | Variation in off<br>current    |

| $T_{fin}$                     | Fin thickness             | $\sigmaig(I_{on}/I_{o\!f\!f}ig)$ | Variation in<br>current ratio  |

| $H_{\it fin}$                 | Fin height                | $NM_H$                           | High state noise margin        |

| $t_{ox}$                      | Oxide thickness           | $NM_L$                           | Low state noise margin         |

| $L, L_g$                      | Gate/channel<br>length    | $\overline{\phi}$                | Average grain size             |

| Ω                             | Wave function             | $Q_{inv}$                        | Inversion charge               |

#### INTRODUCTION

#### 1.1 Introduction

To get increased packing density, the dimensions of devices are reduced. Smaller device size enables higher device density in an integrated circuit. Hence the scaling down of the dimensions of MOSFETs (metal-oxidesemiconductor field-effect transistors) has been a continuous trend since their inception. As devices are scaled down, the influences from side regions and leakage currents become significant. Therefore, device longchannel approximations are no longer valid. In long-channel devices, the influence of electric fields emanating from the source/drain regions are much less important than those coming from the gate, since the center of the channel is far from the source/drain region, and the edge of the channel is only a small portion of the intrinsic part of the device. However, it is well known that this is no longer valid for devices with present-day technologies. To calculate the threshold voltage in these cases, the full multidimensional charge balance must be considered. This can have a significant impact on the threshold voltage values. In practice, shortchannel effects (SCEs) provide the lower limit of achievable channel lengths for a given technology. SCEs tend to lower the threshold voltage for short-channel devices. This leads to larger I<sub>OFF</sub> and higher power consumption.

This introductory chapter gives a brief outline of the SCEs in MOSFETs.

#### 1.2 Short-Channel Effects

Various important SCEs in MOS transistors are channel-length modulation, threshold voltage roll-off, drain-induced barrier lowering (DIBL), bulk punchthrough, tunneling leakage currents, and velocity saturation.

#### **Channel-length Modulation**

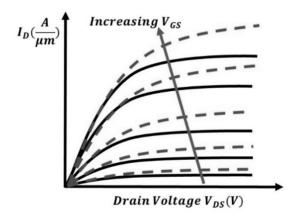

Channel-length modulation in a MOSFET is the first of all SCEs historically observed. It is due to the increase of the depletion layer width at the drain with increased drain voltage [1]. This leads to a shorter channel length and an increased drain current (Fig. 1.1). The channel-length-modulation effect typically increases in small devices with low-doped substrates. An extreme case of channel-length modulation is punchthrough, where the channel length reduces to zero. Proper scaling can reduce channel-length modulation, namely by increasing the doping density as the gate length reduces [1].

**FIGURE 1.1** Current-voltage characteristics of a MOSFET with (dotted) and without (solid) channel-length modulation for different gate voltages

### **Threshold Voltage Roll-off**

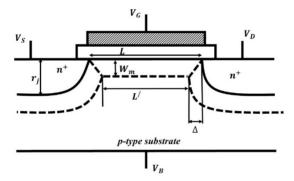

When the edge effects are enhanced, the depletion width for the drain junction is almost equal to that for the source junction. Since the channel-depletion region overlaps the source and the drain-depletion regions, the charge induced by the gate bias field can be approximated within the

trapezoidal region as shown in Fig. 1.2. The threshold roll-off is given by [2],

$$\Delta V_T = \frac{q N_A W_m r_j}{C_{ox} L} \left[ \sqrt{1 + \frac{2W_m}{r_j}} - 1 \right]$$

Where  $N_A$  is the acceptor concentration,  $W_m$  is maximum depletion width,  $C_{ox}$  is oxide capacitance, q is the electron charge and  $r_j$  is the junction depth.

**FIGURE 1.2** Two-dimensional schematic of a MOSFET showing the parameters responsible for threshold voltage roll-off

#### **Drain-Induced Barrier Lowering**

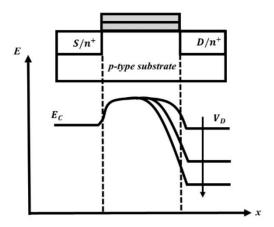

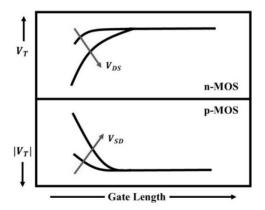

When the gate voltage is below the threshold voltage  $V_T$ , the p-Si substrate forms a potential barrier between n+ source and drain. For short-channel devices, the applied potential at the drain pulls down this barrier. This effect becomes more prominent when the device works in the saturation region due to a large drain voltage with a significantly wider drain junction depletion layer depth. This barrier lowering effect leads to a substantial increase in electron injection from source to the drain, resulting in an enhanced drain current [3]. This effectively reduces the threshold voltage further. With the increase of drain voltage, the conduction band energy is lowered as observed in Fig. 1.3. The threshold voltage roll-off is seen for around 2  $\mu$ m gate length. The change in drain voltage causes the variation in threshold voltage for short-channel devices as shown in Fig. 1.4.

FIGURE 1.3 Effect of Drain induced Barrier Lowering on conduction band edge

FIGURE 1.4 Threshold voltage roll-off with gate length

### **Bulk Punchthrough**

If the drain voltage is large enough, a significant amount of leakage current flows from drain to source via the bulk of the substrate in a short-channel MOSFET. The gate can no longer turn the device completely off and loses its control over the channel [4, 5]. Moreover, high leakage current limits device performance for short-channel MOSFETs, as shown in Fig. 1.5.

FIGURE 1.5 Effect of punchthrough

#### **Tunneling Leakage Currents**

Quantum mechanical tunneling of carriers through the energy barriers in the device is another limiting factor for the scaling of the MOSFETs, as they increase the leakage currents significantly. Band-to-band (Zener) tunneling between body and drain, direct source-to-drain tunneling current and tunneling from the gate oxide are classified as the three major sources of tunneling leakage currents that come into effect as the device dimensions are scaled down [6, 7].

Leakage currents come primarily from two sources: gate oxide leakage and subthreshold leakage. Fig. 1.6 shows the gate oxide leakage that occurs when electrons jump ("tunnel") from the gate to the channel through the gate oxide. Scaling reduces the thickness of the oxide and the thinner the oxide the higher is the leakage due to tunneling. Subthreshold leakage occurs when a nonzero channel current flows even in the absence of an inversion layer; that is, the gate voltage is below  $V_{th}$  when ideally the channel should be "off". Subthreshold leakage becomes worse as  $V_{th}$  is lowered due to SCEs in scaled-down devices.

FIGURE 1.6 Tunneling leakage currents

#### **Gate-Induced Drain Leakage Current**

Due to the reduction of the MOSFET gate oxide thickness, the fields in both the oxide and silicon in the gate-drain overlap region increase. The large fields deplete the drain overlap region, leading to significant band bending. This leads to a band-to-band tunneling current in the gate-overlap, deepdepleted drain regions. This gate-induced drain leakage (GIDL) current has been well observed in conventional MOSFETs and seen as degradation of short-channel performance and leakage currents [8]. The GIDL current is strongly dependent on gate and drain bias. As the MOSFET channel length is scaled down, the nonscalability of the overlap region further degrades the device performance. The GIDL current, however, strongly depends on the doping profile of the drain. For very high drain doping, even though the depletion width is very narrow, the FERMI potential (E<sub>F</sub>) gets pinned, which in turn prevents band bending at the oxide-silicon interface and hence suppresses the tunneling leakage currents. For low drain doping, even though the band bending is significant, the depletion width is too wide to cause any significant tunneling current. Therefore, the GIDL currents exist only within a certain doping range.

#### **Gate Oxide Leakage Current**

To minimize SCEs and maintain constant field in the oxide, in accordance with Dennard's scaling rule, the gate oxide thickness,  $t_{ox}$ , is scaled in proportion to L and W. However, as  $t_{ox}$  is scaled, tunneling leakage current

through the oxide comes into the picture and starts increasing [9, 10]. It has been shown that the silicon dioxide can be thinned down to slightly below 2 nm before the leakage currents are large enough to become unacceptable. The tunneling takes place not only in the inversion layer but also in the accumulation region, as well as the region where the gate overlaps the source and the drain. As a result, the latter component becomes significant in a scaled device. A possible solution to reduce the direct tunneling through the insulator is the use of physically thicker gate dielectric material with relative dielectric constant,  $\mathcal{E}$ , higher than that of silicon dioxide. However, the thickness cannot grow to an unlimited limit as two-dimensional effects in the thicker insulator start to interfere with scaling. Therefore, the short-channel performance is degraded due to the fringing fields from the source and the drain regions, which become non negligible as the thickness-to-length aspect ratio increases [11].

#### **Velocity Saturation**

FIGURE 1.7 Velocity saturation effect is shown

In a short-channel device, the longitudinal electric field is no longer negligible compared to the transverse field. In terms of drain current under normal device operation, the most significant effect is the effective reduction of mobility with the increasing longitudinal field [12]. Fig. 1.7 illustrates the behavior of drift velocity  $v_d$  with electrical field (E). The velocity of carriers in the inversion layer tends to saturate at high E values.

Effects due to lack of proportionality between  $v_d$  and  $\it E$  on device characteristics are referred to as velocity saturation effects. In this regard, we have [12],

$$v_d \approx \mu |E|; \; |E| \leq E_c$$

$$\approx |v_d|_{max}; \; |E| > E_c$$

and  $E_c = \frac{|v_d|_{max}}{\mu}$  where  $E_c$  is known as the critical electric field.

### 1.3 Scaling Rules in MOSFETs

As the device dimensions are miniaturized, the SCEs must be minimized to maintain device integrity. Some guidelines are required in scaled-device design. The term scaling denotes "the possibility of fabricating functional devices with equally good or even improved performance matrices but smaller physical dimensions" [13]. "One elegant approach for maintaining the long-channel behavior is to simply reduce all dimensions and voltages by a scaling factor  $\alpha(>1)$ , so that the internal electric fields are the same as those of a long-channel MOSFETs. This approach is called "constant field scaling". Scaling is also possible without making any change to the supply voltage [14]. Table 1.1 summarizes the scaling rules of constant-field scaling for various device parameters and circuit performance factors. The circuit performance, i.e., speed and power consumption in the on state, can be enhanced as the device dimensions are scaled down. In practical integrated circuit manufacturing, however, the electric fields inside the smaller devices are not kept constant but allowed to increase to some extent. This is mainly because the power supply and  $V_T$  cannot be scaled arbitrarily. If the threshold voltage is too small, the leakage level in the off state  $(V_G = 0 V)$  will increase significantly because of the nonscalable subthreshold swing. Consequently, standby power consumption will also increase. By applying the scaling rules, MOSFETs have been fabricated having channels as short as 20 nm, a very high transconductance (>1000) mS/mm), and reasonable subthreshold swing (120 mV/decade).

According to the two scaling strategies defined in Table 1.1, all the lateral (primarily the gate width and the length) and the vertical dimensions should decrease from one technology generation to the next by the factor  $\alpha$ , thus yielding an increase of the number per unit chip area by the factor  $\alpha^2$ . The constant field and constant supply voltage scaling rules are derived

from quite simple one-dimensional models of MOSFET electrostatics. These models and the rules became inadequate to the design of MOS transistors as the gate length (L<sub>G</sub>) approaches one micron, thus leading to the development of more sophisticated criteria. As mentioned in Table 1.1 the mixed scaling is proposed in [15] to design 0.25µm MOSFETs, where different reduction factors are introduced for the geometrical dimensions ( $\alpha$ ) and the voltages ( $\lambda$ ). Since the thermal voltage kT/q, the band and the junction built-in voltage do not scale, the subthreshold swing of the transfer characteristics and the flat band voltage of Poly-silicon gate MOSFET remain almost invariant to scaling [16]. As a result, the two-dimensional distribution of electrostatic potential inside the scaled device is distorted compared to that of the parent technology generation and so-called SCEs become apparent.

TABLE 1.1. Scaling rules for Complemenatry MOSFET (CMOS) technology

| MOSFET device and circuit parameters  Device dimensions ( <i>d</i> , <i>L</i> , <i>W</i> , <i>r<sub>j</sub></i> ) | Constant field scenario 1/α | Constant voltage Scenario 1/α | Mixed scenario       |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|----------------------|

| Doping concentration (N <sub>A</sub> , N <sub>D</sub> )                                                           | α                           | α <sup>2</sup>                | $\alpha^2/\lambda$   |

| Voltage (V)                                                                                                       | 1/α                         | 1                             | 1/λ                  |

| Electric field (E)                                                                                                | 1                           | α                             | α/λ                  |

| Current (I)                                                                                                       | 1/α                         | α                             | $\alpha/\lambda^2$   |

| Gate capacitance (C)                                                                                              | 1/α                         | 1/α                           | 1/α                  |

| Oxide capacitance ( $C_{ox}$ )                                                                                    | α                           | α                             | α                    |

| Interconnect resistance                                                                                           | α                           | α                             | α                    |

| Circuit delay time ( $\tau$ )                                                                                     | 1/α                         | $1/\alpha^2$                  | $\lambda/\alpha^2$   |

| Power dissipation per circuit(P)                                                                                  | 1/α²                        | α                             | 1                    |

| Power delay product per circuit (P, τ)                                                                            | 1/α³                        | 1/α                           | $1/\alpha^2\lambda$  |

| Power density (P/A)                                                                                               | 1                           | α 3                           | $\alpha^3/\lambda^3$ |

Note:  $\alpha$  and  $\lambda$  denote the geometry and voltage scaling factors.

#### 1.4 Control of SCEs in MOSEFTs

An optimum choice of channel doping, the junction depth and the thickness of the gate dielectric is crucial to keep SCEs under control. Accurate tailoring of the source and drain extensions below the spacers and reduction of parasitic source/drain resistances contribute as well to achieving good performance and high I<sub>ON</sub>/I<sub>OFF</sub> ratios. As a consequence of the increased complexity of this optimization task, during the 1980s two-and three-dimensional CAD tools for numerical device simulation [17] found widespread use in the semiconductor industry to assist process engineers in analysis and tuning of the doping profiles to counteract SCEs. Studies on the scaling of CMOS technology have emerged from the joint efforts of associations such as the US Semiconductor Industry Association and, later, the International Technology Roadmap for Semiconductors (ITRS). The guidelines documents on MOSFET scaling prepared by the ITRS [18] aim at the early identification of risk factors in the development of the microelectronics industry.

Nowadays, the diversion of microelectronic applications has led to differentiation of the ITRS for high performance (HP), low power (LP) and low standby power (LSTP) [19]. Recently, all the roadmaps for the bulk MOSFET architecture have shared a common difficulty in finding the balance in the trade-off involving the containment of SCEs (which demands high channel doping and gate dielectrics with small equivalent oxide thickness (EOT)), the guest for high on current (which requires high carrier mobility and low threshold voltage), and the need for low subthreshold leakage (which requires high threshold voltage, low subthreshold, low subthreshold swing and relatively thick gate dielectrics). The performance matrices of bulk MOSFET technology have steadily improved. But for the channel-length sub 0.1µm range, it became increasingly difficult to maintain the historical scaling trends by mere optimization of the conventional architecture. The introduction of significant innovations has always been deferred till the time when no real alternative was possible due to complexity and cost. In this respect the replacement of SiO<sub>2</sub> is proposed. SiO<sub>2</sub> has ideal interface properties, large band gap, low trap density etc. The prolonged usability of the most popular dielectric in silicon microelectronics, nitride SiO<sub>2</sub> layers (SiON), were adopted first [20], with undebatable advantages in terms of increased dielectric constant and beneficial effects against boron penetration in p-MOSFETs. With the

advent of 45 nm technology, the first breakthrough innovation at the heart of the bulk MOSFET architecture, the introduction of high-k dielectrics has started to become a reality [21, 22]. It has become clear that significant innovations will be necessary to make the ultimate MOS a reality. Consistently, the technology boosters and new device concepts have been identified by the ITRS to flank the traditional dimension, doping, and voltage scaling. These new options could give significant advantages in terms of intrinsic device performance, thus allowing microelectronics to maintain progress according to the so-called Moore's law.

#### 1.5 Tunnel FET

Unlike the conventional MOSFET, the transport mechanism in tunnel FETs (TFETs) is based on band-to-band tunneling at the source-channel carrier injection (tunneling currents for both the subthreshold region as well as the superthreshold region of operation). The gate length can be scaled down to the tunneling barrier width as small as 10 nm, or even less than this, because tunneling takes place over a very small region [21, 22].

TFETs can be scaled down to ultra-short-channel region without any significant change in device characteristics. The device parameters are independent of the channel length; therefore, statistical variation of the threshold voltage, OFF- and ON- currents, respectively, with channel-length variation are absent. TFETs show reliable operation at both low and high temperatures because of the weak temperature dependence. The current-voltage characteristics is not limited by the thermal factor,  ${}^{kT}/q$ . This allows the thermal limit of the conventional MOSFET to be overcome, like bringing down the subthreshold swing below 60 mV/dec at room temperature [23, 24].

As conventional MOSFETs are scaled down to ultra-short-channel region, tunneling from heavily doped junctions results in large parasitic leakage currents. The on-current of TFET is determined by tunneling and therefore tunneling is no longer an unwanted parasitic effect. Furthermore, the current increases exponentially in both on- and off-regions of operation with respect to conventional device [24, 25]. Explanation of the working of TFETs is outlined in Chapter 2.

#### 1.6 FinFFT

The Fin Field-effect Transistor (FinFET) [26] is one of the competitors that can overcome the undesirable SCEs. It can replace the traditional MOSFET for low power applications [27]. Gate in a FinFET controls the channel from more than one side and provides outstanding performance against SCEs and very high on to off current ratio.

Fig. 1.8 shows the three-dimensional schematic of a FinFET. The main feature of the FinFET is that its conducting channel is wrapped by a thin silicon fin from which it gains its name. The thickness of the fin determines the effective channel of the device. It has a vertical fin between large source and drain. The gate is placed at right angle to the fin and wraps over the whole fin. As such, FinFET is a three-dimensional structure in general, where the gate controls the channel from all the three sides. It can be classified as a multi-gate MOSFET. As expected, it has improved SCEs than planar MOSFETS [26, 28].

FIGURE 1.8 Three-dimensionalview of conventional FinFET

A special property of FinFET is fin width quantization, which says that the width can be increased by using multiple fins. The total transistor width of FinFET is expressed by [28]:

$$W = T_{Si} + 2 H_{fin}$$

where  $T_{Si}$  and  $H_{fin}$  are the fin thickness and fin height, respectively. The total fin width for a FinFET having n parallel vertical fins is given b

$$W = n \times \left(T_{Si} + 2H_{fin}\right)$$

The working principle of a FinFET is similar to that of a MOSFET. The channel shows maximum conductance when there is no voltage on the gate terminal. As the voltage changes to positive or negative, the conductivity of the channel reduces. MOSFETs control the flow of voltage and current between the source and drain terminals. A high-quality capacitor is formed by the gate terminal. For n-MOSFETs, the semiconductor surface at the below oxide layer which is located between source and drain terminal is inverted from p-type to n-type by applying a positive gate voltage [28, 29].

When a small amount of voltage is applied to this structure, at positive gate to source voltage, a depletion region is formed. This depletion region is formed at the interface between Si and SiO<sub>2</sub>. The positive voltage applied attracts electrons from the source terminal, and this forms the electron reach channel [29]. If we apply a voltage between the source and drain terminal, current will flow between source and drain terminals.

#### References

- [1] W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, A. Bryant, O. H. Dokumaci, A. Kumar, X. Wang, J. B. Johnson, and M. V. Fischetti, "Silicon CMOS devices beyond scaling," *IBM J. Res. Dev.*, vol. 50, no. 6, pp. 339–361, 2006.

- [2] E. P. Vandamme, P. Jansen, and L. Deferm, "Modeling the subthreshold swing in MOSFET's," *IEEE Electron Device Lett.*, vol. 18, no. 8, pp. 369–371, Aug. 1997.

- [3] A. Godoy, J. A. López-Villanueva, J. A. Jiménez-Tejada, A. Palma, and F. Gámiz, "A simple subthreshold swing model for short channel MOSFETs," *Solid-State Electron.*, vol. 45, no. 3, pp. 391–397, Mar. 2001.

- [4] Y. Tsividis, Small-Dimension Effects in Operation and Modeling of the MOS Transistor, 2nd ed. New Delhi, India: Oxford University Press, 2011, pp. 248–310.

- [5] Q. Xie, C. J. Lee, J. Xu, C. Wann, J. Y. C. Sun, and Y. Taur, "Comprehensive Analysis of Short-Channel Effects in Ultrathin SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1814–1819, June 2013.

- [6] Donald A. Neamen, *Semiconductor Physics and Devices*, 3rd ed. India: McGraw-Hill, 2003.

- [7] K. Roy, S. Mukhopadhyay, and H. M. Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proc. of the IEEE*, vol. 91, no. 2, pp. 305–327, April 2003.

- [8] C. T. Shah, "Characteristics of the Metal Oxide Semiconductor Transistors," *IEEE Trans. on Electron Devices*, vol. 11, no. 7, pp. 324–345, 1964.

- [9] J. S. Kilby, "Miniaturized electronics circuits," U.S. Patent 3138 743, 1964.

- [10] C. C. Hu, *Modern Semiconductor Devices for Integrated Circuits*. Upper Saddle River, NJ: Prentice Hall, 2010.

- [11] R. H. Dennard, F. H. Gaensslen, L. Kuhn, and H. N. Yu, "Design of micron MOS switching devices," *IEDM Dig. Tech. Paper*, pp. 344, 1972.

- [12] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. I. Rideout, E. Bassous, and A. R. Leblanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE J. Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, 1974.

- [13] David Esseni, Pierpaolo Palestri, and Luca Selmi, *Nanoscale MOS Transistors: Semi-Classical Transport and Applications*. Cambridge: Cambridge University Press, 2011.

- [14] R. H. Dennard, F. H. Gaensslen, E. J. Walker, and P. W. Cook, "1 µm MOSFET VLSI technology: Part II-Device design and characteristics for high-performance logic applications," *IEEE J. Solid-State Circuits*, vol. 26, no. 4, pp. 325–332, 1979.

- [15] Sentaurus Device User Manual, Synopsys, 690E Middlefield Road, Mountain View, CA 94043, 2009.

- [16] "International Technology Roadmap for Semiconductors", http://public.itrs. net/, 2013 ed.

- [17] S. Zhu, A. Nakajima, T. Ohashi, and H. Miyake, "Bias Temperature Instability in MOSFETs with Atomic-Layer-Deposited Si-Nitride/SiO2 Stack Gate Dielectrics," 2006 8th International Conference on Solid-State and Integrated Circuit Technology Proceedings, Shanghai, 2006, pp. 1126–1128.

- [18] Nirmal, V. Kumar, P. C. Samuel, Shruthi, D. M. Thomas and M. Kumar, "Analysis of dual Gate Mosfets using high k

- dielectrics," 2011 3rd International Conference on Electronics Computer Technology, Kanyakumari, 2011, pp. 22–25.

- [19] N. Kumari and S. Meena, "Analysis of various parameters of double gate junctionless MOSFET using Ge-source with High-k Spacer," 2017 International Conference on Computing, Communication and Automation (ICCCA), Greater Noida, 2017, pp. 1453–1456.

- [20] G. E. Moore, "Cramming more components onto integrated circuits", *Electronics*, vol. 38, no. 8, pp. 114ff., Apr. 1965.

- [21] W. Choi, B. G. Park, J. D. Lee, and T. J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec", IEEE Electron Device Lett., vol. 28, no. 8, pp.743–745, 2007.

- [22] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches", *Nature*, vol. 479, pp. 329–337, Nov. 2011.

- [23] A. Villalon, G. Le Carval, S. Martinie, C. Le Royer, M.-A. Jaud, and S. Cristoloveanu, "Further Insights in-TFET Operation", *IEEE Trans. Elect. Dev.*, vol. 61, no. 8, pp. 2893–2898, 2014.

- [24] P. F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, Ch. Stepper, M. Weis, D. S. Landsiedel, and W. Hansch, "Complementary tunneling transistor for low power application," *Solid State Electronics*, vol. 45, pp. 2281–2286, 2004.

- [25] C. L. Royer and F. Mayer, "Exhaustive experimental study of tunnel field effect transistors (TFETs): From materials to architecture," *Proc. 10th Int. Conf. ULIS*, pp.54–56, 2009.

- [26] D. Bhattacharya and N. K. Jha, "FinFETs: from Devices to Architectures," Article ID 365689, Hindawi Publishing Corporation, *Advances in Electronics*, p. 21, 2014.

- [27] C. Yadav, P. Kushwaha, S. Khandelwal, J. P. Duarte, Y. S. Chauhan, and C. Hu, "Modeling of GaN-Based Normally-Off FinFET," *IEEE Electron Device Lett.*, vol. 35, no. 6, pp. 612–614, June 2014.

- [28] G. Pei, J. Kedzierski, P. Oldiges, M. leong, and E. C.-C. Kan, "FinFET design considerations based on 3-D simulation and analytical modeling," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1411–1419, 2002.

- [29] R. Rios et al., "Comparison of Junctionless and Conventional Trigaten Transistors with Down to 26 nm," *IEEE Electron Device Lett.*, vol. 32, no. 9, pp. 1170–1172, Sept. 2011.

## **DEVICE ARCHITECTURES: TFETs AND FINFETs**

#### 2.1 Introduction

This chapter presents a general survey on the different architectures of TFETs and FinFETs. TFETs and FinFETs have emerged as alternatives to MOSFETs due to their ability to withstand scaling. Scaled MOSFETs depict deteriorating performance with high leakage currents and poor subthreshold swings. While TFETs which operate on interband tunnelling can achieve theoretical subthreshold swings below 60 mV/dec, FinFETs, which are structural modifications of MOSFETs, can have reduced subthreshold swing as well, due to the greater influence of the gate on the fin structure. This chapter briefly explores some of the architectures of both devices in order to provide to readers an overview of the existing styles of geometry.

#### 2.2 TFET Architectures

### **Geometry of Conventional TFETs**

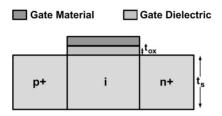

A conventional TFET geometry is shown in Fig. 2.1. The biasing conditions for *p*-type and *n*-type TFETs are tabulated in Table 1.1.

In an n-TFET, the application of positive gate voltage suppresses the energy bands at the *p+*-source- *i*-channel junction, causing the valence band of the source to line up with the conduction band of the channel. The tunnel barrier is approximated as a triangular barrier with reduced tunnel width [1]–[3]. The electrons from the valence band of the source tunnels through the barrier into the conduction band of the channel, and are finally collected by the *n+*-drain through a positive bias.

This mechanism of transport in TFETs allows them to possess SS lesser than the thermal limit of 60 mV/dec in MOSFETs. The tunnel barrier acts as a filter that prevents the passage of high and low energy Fermi tails, whereas

in MOSFETs thermionic emission allows the transmission of high-energy Fermi tails. TFETs also exhibit low off current due to their carrier transport mechanism [1]. SCEs are minimized owing to the dependence of the total current on the tunnel current concentrated at the tunnel junction. The advantage of TFETs is its compatibility with CMOS fabrication techniques.

FIGURE 2.1 Geometry of a conventional TFET

**TABLE 2.1** Modes of operation in TFETs, convention of source and drain regions and biasing conditions

| Mode of Operation | Source | Drain | Bias                     |

|-------------------|--------|-------|--------------------------|

| <i>p</i> -type    | n+     | p+    | $V_{GD} < 0; V_{SD} < 0$ |

| <i>n</i> -type    | p+     | n+    | $V_{GS} > 0; V_{DS} > 0$ |

#### **Evolution of TFETs**

The idea of TFETs was first conceptualized by Stuetzer in 1952 before the invention of Esaki tunnel diodes, when he fabricated a p-n junction and explained its principle of operation under conditions of reverse bias [4]. He termed it "fieldistor". His paper discussed the effect of the position of the control electrode on the device characteristics, showing the presence of ambipolarity in the device. In 1977, Quinn et al. proposed the idea of a surface tunnel junction by substituting the degenerate n-type source of a MOSFET by a highly degenerate p-type source [5]. The paper mentioned the requirement of an abrupt junction and maximum band bending. The main focus of the work was subband splitting near to the tunnel junction, and the scope of determining the phenomenon experimentally. In 1987, Banerjee et al. presented a three-terminal device and reported the presence of Zener tunneling in the device [6]. The authors calculated the tunneling current by approximating the shape of the tunnel barrier as triangular. Takeda et al. proposed and characterized a band-to-band tunneling MOS device, and highlighted the negligible SCEs associated with

the 'Silicon quantum device' [7]. In 1992, Baba proposed the surface tunnel transistor (STT), an alternative version of Quinn's device, where he commented on the use of a gate to control negative differential resistance (NDR) in the forward bias state [8]. In 1995, Reddick and Amartunga proposed a gate controlled p+-p-n+ structure of the STT, and produced experimental as well as simulation results to explain interband tunneling in STTs [9]. They also presented the basic formula for barrier height at the tunnel junction, which finds its use in analytical modeling of TFETs. In 1996, Uemura and Baba first demonstrated NDR in two planar-type STTs based on GaAs and InGaAs [10]. The gating of the vertical TFET was proposed by Hansch *et al.* in 2000 [11]. In 2004, the Silicon-on-insulator TFET was first proposed by Aydin *et al.* [12].

#### **Modifications of Tunnel FETs**

This section reports the next phase of development of TFETs after the establishment of fundamental *p-i-n* geometry. The significant architectures of TFETs proposed so far are presented here in brief, along with the types of analyses performed on those architectures. To maintain an organized discussion, a TFET architecture accompanied by modifications or associated improvements is presented in the following paragraphs.

Knoch and Appenzellar proposed the Tunneling Carbon Nanotube FETs in 2004, and discussed the methods to reduce the tunneling probability at the tunnel junction [13]. The one-dimensionality of carbon nanotube results in efficient band-to-band tunneling. A minimum SS of 15 mV/dec was achieved for low drain bias in the band-to-band tunneling regime.

Boucart and Ionescu proposed Double-Gate TFETs [14, 15] by introducing two gate terminals, one on the front and the other on the back, thus increasing the influence on the tunnel junction. The device was reported to offer a boosted on current as high as 0.23 mA, improved off current less than 1 fA and sub-60 mV/dec SS equal to 57 mV/dec. Toh *et al.* proposed a DG TFET with a silicon germanium source to modulate the tunnel barrier at the tunnel junction, thus resulting in enhanced on-current and sub-kT/q subthreshold swing [16]. DG TFETs using an InAs/Si heterojunction at the source-channel tunnel junction were reported by Ahish *et al.* to reduce the tunnel window and boost the on current [17].